Uploads by RSS1

This special page shows all uploaded files.

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

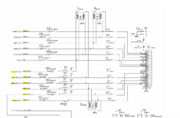

| 21:12, 26 April 2026 | DIF-AT MAIN.JPG (file) |  |

6.28 MB | Main board full | 1 |

| 21:13, 26 April 2026 | TDIF-BOARD.JPG (file) |  |

6.16 MB | TDIF daughter board. | 1 |

| 21:17, 26 April 2026 | ALESIS OTP CPLD.JPG (file) |  |

5.78 MB | Not sure if this is OTP GAL/CPLD. Custom. | 1 |

| 21:18, 26 April 2026 | SRAM + NOR FLASH.JPG (file) |  |

5.7 MB | Sram and NOR flash chip (512kb) | 1 |

| 21:20, 26 April 2026 | Main Board Side On.JPG (file) |  |

5.45 MB | main board different angle (missing ICs now) | 1 |

| 21:22, 26 April 2026 | H8 3005 CPU.JPG (file) |  |

4.74 MB | Roland used a full cpu for this design. | 1 |

| 21:23, 26 April 2026 | Binwalk entropy image.png (file) |  |

68 KB | Binwalk entropy file for firmware | 1 |

| 21:24, 26 April 2026 | HEW.png (file) |  |

917 KB | High performance embedded workshop RAM settings for firmware. | 1 |

| 21:40, 26 April 2026 | DIFAT 24.jpg (file) |  |

100 KB | 1 | |

| 08:55, 27 April 2026 | DIF AT FLASH SETTINGS.png (file) |  |

689 KB | 1 | |

| 12:39, 27 April 2026 | DIFat 50 pin header1 .png (file) |  |

554 KB | pins 1 to 16 on the header | 1 |

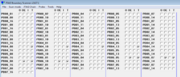

| 12:40, 27 April 2026 | DIFat 50 pin header2.png (file) |  |

501 KB | pins 16-24 on the header | 1 |

| 12:41, 27 April 2026 | DIFat 50 pin header3.png (file) |  |

452 KB | pins 25 -38 on the header | 1 |

| 12:43, 27 April 2026 | DIFat 50 pin header4.png (file) | 203 KB | pins 38 -50 on the header | 1 | |

| 13:47, 27 April 2026 | DIFAT PIN HEADER GENERAL NOTES.png (file) |  |

452 KB | General notes about the CPU,Flash, SRAM operational pins | 1 |

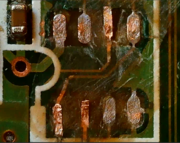

| 16:47, 27 April 2026 | Sync section optocouplers.JPG (file) |  |

5.89 MB | Part of the sync circuitry with optocouplers | 1 |

| 16:49, 27 April 2026 | 5v conditioning circuit.jpeg (file) |  |

4.66 MB | power conditioning | 1 |

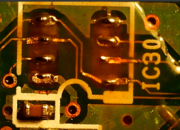

| 16:53, 27 April 2026 | Reset circuit.jpg (file) |  |

4.71 MB | reset IC and switch | 1 |

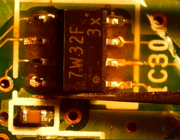

| 16:56, 27 April 2026 | Xilinx CPLD.jpg (file) |  |

5.6 MB | Xilinx CPLD and mux circuit. JTAG pads visible around pin 50 (silkscreen) and 81. | 1 |

| 18:23, 27 April 2026 | VIVERIS BOUNDARY SCANNER.png (file) |  |

439 KB | 1 | |

| 18:31, 27 April 2026 | XC3SPROG id read.png (file) |  |

257 KB | XC3SPROG_id_read screenshot. | 1 |

| 18:32, 27 April 2026 | Pullup info.png (file) |  |

1.01 MB | pullup info, essential to correct read! | 1 |

| 18:33, 27 April 2026 | Bluetag pin read.png (file) |  |

283 KB | bluetag determines correct pinout | 1 |

| 18:34, 27 April 2026 | Open OCD.png (file) |  |

979 KB | OpenOCD reads CPLD | 1 |

| 20:23, 27 April 2026 | DIF-AT BINVIS.png (file) |  |

1.2 MB | DIF AT BINVIS representation. | 1 |

| 08:46, 28 April 2026 | DIFAT CUTTER SSHOT.png (file) |  |

1.09 MB | 1 | |

| 09:47, 28 April 2026 | DIF AT RBUS CONNECTOR SCHEMATIC.png (file) |  |

524 KB | 1 | |

| 10:28, 28 April 2026 | Dif-at-tracerepair.png (file) |  |

4.51 MB | dif at trace repair | 1 |

| 10:29, 28 April 2026 | Dif-at-tracerepair2.png (file) |  |

3.91 MB | dif at trace repair tinned fluxed | 1 |

| 10:30, 28 April 2026 | Dif-at-tracerepair3.png (file) |  |

3.47 MB | dif at trace repair place component | 1 |

| 10:39, 28 April 2026 | Dif-at-tracerepair4.png (file) |  |

4.48 MB | heres the CPU with some 16 traces repaired. Sorry, not a great shot. | 1 |